回应模式 - No.64668766

No.64668766 - 社畜

无标题无名氏No.64668766 只看PO

2024-12-12(四)09:34:30 ID:xgpSNV8 回应

校招稀里糊涂进了车企供应商开发岗已经三年半了,总之先放一个串在这里

|д` )目前做嵌入式底层Mcal,有想问的也可以问

无标题无名氏No.65313238

2025-02-18(二)10:27:31 ID: xgpSNV8 (PO主)

>>No.65313120

( ゚π。)上次有个那种八竿子打不着的bug,直接跳过所有分析直接来质问是不是我的问题

这种是真难评( ´_ゝ`)

无标题无名氏No.65313245

2025-02-18(二)10:29:09 ID: xgpSNV8 (PO主)

>>No.65308609

今天跟同事讨论了一下,可能还是adc往dma送值这段出现了问题

但领导想降低优先级( ´_ゝ`)

等我干完手头的活再想想

无标题无名氏No.65315457

2025-02-18(二)16:09:52 ID: iOTYiIy

>>No.65313238

比起BUG更恐怖的是解决不了的bug

更好的消息是我有三个项目,三倍的bug( ´д`)

无标题无名氏No.65315631

2025-02-18(二)16:31:46 ID: xgpSNV8 (PO主)

>>No.65313245

大概写了一下昨天测试log的分析(*゚ー゚)

还好这个base很好,DMA传递ADC之后会顺便记一次TIM时间戳,这个时间戳对应相关ADC的触发源。

看来是一个周期两次采样里只记录了某一次,还挺固定的吧,拉了一下时间轴,没有正常的。

无标题无名氏No.65324545

2025-02-19(三)17:34:38 ID: xgpSNV8 (PO主)

>>No.65315631

忙了半天,摸了半天,突然把这个问题搞定了| ω・´)更新前因后果?

昨天查到DMA记录的TIM时间戳,更新一次加2个边沿计数。但配置里配的是双边沿均触发采样,这显然有问题,最有问题的肯定还是我的手写代码部分。

Q2的特殊性可以通过把Q2的采样放到Q1测试,排除。

ADC资源不够可以通过禁止其他队列测试,排除。

这差不多是今天早上查到的地方。

无标题无名氏No.65324596

2025-02-19(三)17:40:57 ID: xgpSNV8 (PO主)

>>No.65324545

参考了base的channel入队代码,发现comment里说只有队列的第一个channel入队要配external trigger。

抄了一下,好了( ゚ 3゚)但没想通为啥是现在这种采了一半的状况。

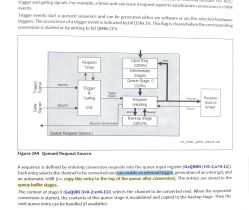

然后就去看手册,大概理解一下这张图和内容。一个队列接到一个触发后,第一个采完,第二个channel并不需要一个额外的触发,所以轮到它就会进行采样。| ω・´)

这样跑到队尾,因为配了RF(自动填充,这里没有明确去验证),会自动回到第一个,继续等待下一个触发。

所以如果两个channel都配额外触发源,采完一个,第二个一定会等下一个触发来了再采。( ゚ 3゚)完结撒花!等同事帮我测试咯~

无标题无名氏No.65334824

2025-02-20(四)19:49:06 ID: xgpSNV8 (PO主)

( ゚ᯅ 。)不行了,被几个同事轮流叫去看问题,还加了班

现在一听到我名字就条件反射的咯噔

无标题无名氏No.65334855

2025-02-20(四)19:52:08 ID: xgpSNV8 (PO主)

( ゚ᯅ 。)今天就有个新问题是新配的CAN不通。我查了状态机没问题,操作CAN芯片的引脚不确定好不好,总之高低电平都试了一下。

高电平场合,接收状态是idle

低电平场合,接收状态是receiver...但PSR是报form error的|д` )

因为被打断了,总之现在问题也就查到这儿,明天再说!